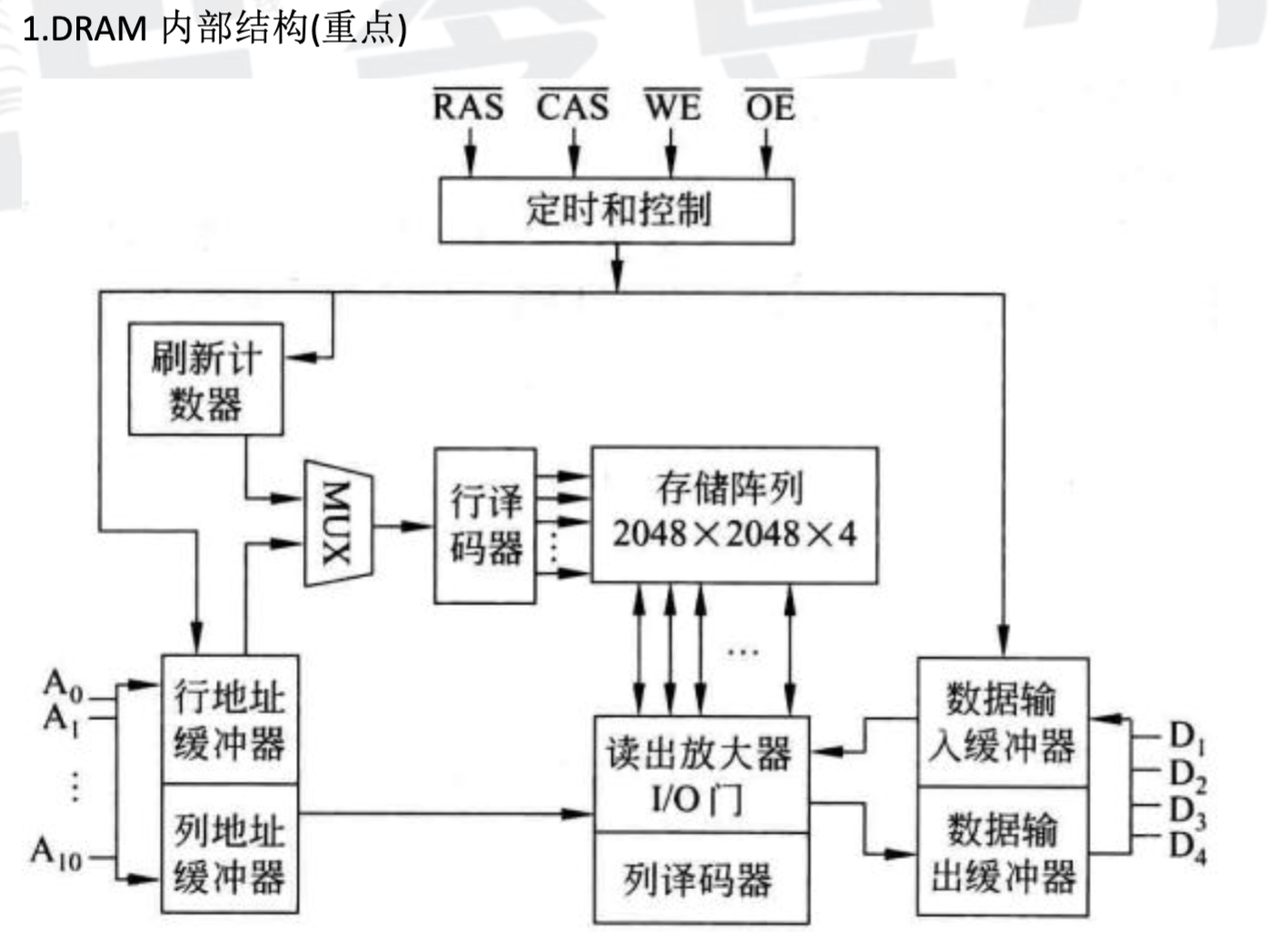

一、 DRAM 内部结构图解读

1. 核心部件分析

-

定时和控制 (Timing and Control): 这是DRAM的大脑。它接收外部控制信号,并生成所有内部操作所需的时间序列和控制逻辑。

-

RAS (Row Address Strobe, 行地址选通): 低电平有效。当RAS信号下降时,DRAM会锁存(Latch)地址线上的信号作为行地址。

-

CAS (Column Address Strobe, 列地址选通): 低电平有效。当CAS信号下降时,DRAM会锁存地址线上的信号作为列地址。

-

WE (Write Enable, 写使能): 控制读写模式。WE为低电平时为写操作,高电平时为读操作。

-

OE (Output Enable, 输出使能): 控制数据输出缓冲器。只有在读操作且OE有效时,数据才会被驱动到数据引脚上。

-

-

地址输入 (A₀ ~ A₁₀): 如图所示,该芯片有11条地址线。通过地址复用技术,这11条线既可以传输行地址,也可以传输列地址。

-

地址缓冲器与MUX:

-

行/列地址缓冲器: 临时存储从地址引脚上接收到的行地址和列地址。

-

MUX (Multiplexer, 多路选择器): 这是一个关键部件。它负责选择将哪个地址送入行译码器:是来自地址缓冲器的地址(用于正常读写),还是来自刷新计数器的地址(用于刷新)。

-

-

刷新计数器 (Refresh Counter):

- 这是一个内部计数器,它会自动、依次地生成所有行的地址(0, 1, 2, ..., 2047)。其唯一的目的就是为刷新操作提供行地址。

-

存储阵列 (Storage Array):

2048 × 2048 × 4-

这是DRAM的核心,由我们上一问中讲的1T1C存储元组成。

-

2048 × 2048:表示这个阵列有 2048 行 和 2048 列。这与地址线数量完美对应:211=2048,因此需要11位行地址和11位列地址。 -

× 4:表示这个芯片有4个这样的存储阵列(也称位平面)。当给出一个行、列地址时,会同时在4个阵列的对应位置进行操作,一次可以读/写4位数据。这决定了芯片的数据位宽为4。

-

-

译码器与读出放大器:

-

行译码器 (Row Decoder): 接收11位行地址,从2048条字选择线 (Word Line) 中唯一选中一条,激活一整行的存储元。

-

读出放大器 (Sense Amplifier) / I/O门: 当一行被激活时,这一整行(2048×4个)存储元的数据都会被读入到读出放大器中。读出放大器负责检测微弱的电压信号、将其放大并作为临时缓存。

-

列译码器 (Column Decoder): 接收11位列地址,从读出放大器缓存的一整行数据中,选择出目标列对应的4位数据,并将其连接到数据输入/输出缓冲器。

-

-

数据缓冲器与数据线 (D₁ ~ D₄):

-

数据输入/输出缓冲器: 负责管理数据进出芯片。

-

D₁ ~ D₄: 芯片的4位数据引脚,用于与外部(如内存控制器)交换数据。

-

二、 实例:数据的流动与生命周期

让我们以一个具体的例子,追踪4位数据 1011 在这个DRAM芯片中的完整生命旅程。

假设我们要将数据 1011 写入到由 行地址 5 (二进制 0...00101) 和 列地址 88 (二进制 0...1011000) 指定的单元中,然后再将其读出。

阶段一:写入操作 (数据的诞生)

-

准备阶段: 内存控制器准备好了地址(行5,列88)和数据(

1011)。 -

发送行地址: 控制器将行地址 5 放到地址线

A₀~A₁₀上。 -

RAS 选通: 控制器拉低

RAS信号。DRAM芯片内部的行地址缓冲器立即锁存地址5。 -

行激活: 行译码器解码地址

5,激活存储阵列中的第5条字选择线(Word Line)。此时,第5行所有的2048 × 4个存储元都被连接到各自的读出放大器上,整行数据被载入并暂存其中(这是读操作的前半部分,写操作也需要这一步,称为Read-Modify-Write)。 -

发送列地址: 控制器将列地址 88 放到同样的地址线

A₀~A₁₀上。 -

发送数据: 控制器将数据

1011放到数据线D₁~D₄上。 -

CAS 与 WE 选通: 控制器同时拉低

CAS和WE信号。-

CAS的下降使列地址缓冲器锁存地址88。 -

WE的低电平告知定时和控制单元,这是一个写操作。

-

-

列选择与写入: 列译码器解码地址

88。数据输入缓冲器接收1011,并通过I/O门将其写入到读出放大器中第88列的位置,覆盖了原来暂存的数据。 -

写回存储元: 读出放大器中被更新的数据(

1011)被重新写回到第5行、第88列的4个物理存储电容C_s中。 -

操作结束:

RAS,CAS,WE信号恢复高电平,一次写周期完成。数据1011作为电荷被存储在四个微小的电容器中。

阶段二:静默与刷新 (数据的维生)

-

电荷泄漏: 存储着'1'的电容开始缓慢漏电,电压下降。若不干预,数据将在几十毫秒内丢失。

-

刷新周期: 在数据丢失前,DRAM芯片的定时和控制单元会启动一次刷新。

-

内部刷新计数器提供一个行地址(假设恰好是

5)。 -

MUX切换到刷新计数器通路。 -

控制器执行一个“仅RAS”周期,即只拉低

RAS。 -

行译码器激活第5行,将整行数据(包括我们那个电压已略微衰减的

1011)读入读出放大器。 -

读出放大器将这个衰减的信号重新放大到标准的逻辑高/低电平,并立即写回到原来的存储元中。

-

-

生命延续: 我们的数据

1011被成功“续命”,电容被重新充满。这个过程对外部系统是透明的。

DRAM都会怎么洗澡🥵

阶段三:读出操作 (数据的价值实现)

-

行地址选通: 与写入操作的步骤1-4完全相同。控制器发送行地址

5,RAS下降,第5行的全部内容被读入并暂存在读出放大器中。这个过程也刷新了第5行的数据。 -

列地址选通: 控制器发送列地址

88,然后拉低CAS信号 (WE保持高电平,表示读取)。 -

列选择: 列译码器解码地址

88,从读出放大器中选中暂存的4位数据1011。 -

输出使能: 控制器拉低

OE信号,打开数据输出缓冲器的三态门。 -

数据上路: 数据

1011被驱动到外部数据线D₁~D₄上。 -

读取成功: 内存控制器从数据线上成功读取

1011。 -

操作结束:

RAS,CAS,OE恢复高电平。读周期结束。