单周期和多周期CPU的硬件电路实现区别

区别一:统一的存储器 vs. 分离的存储器

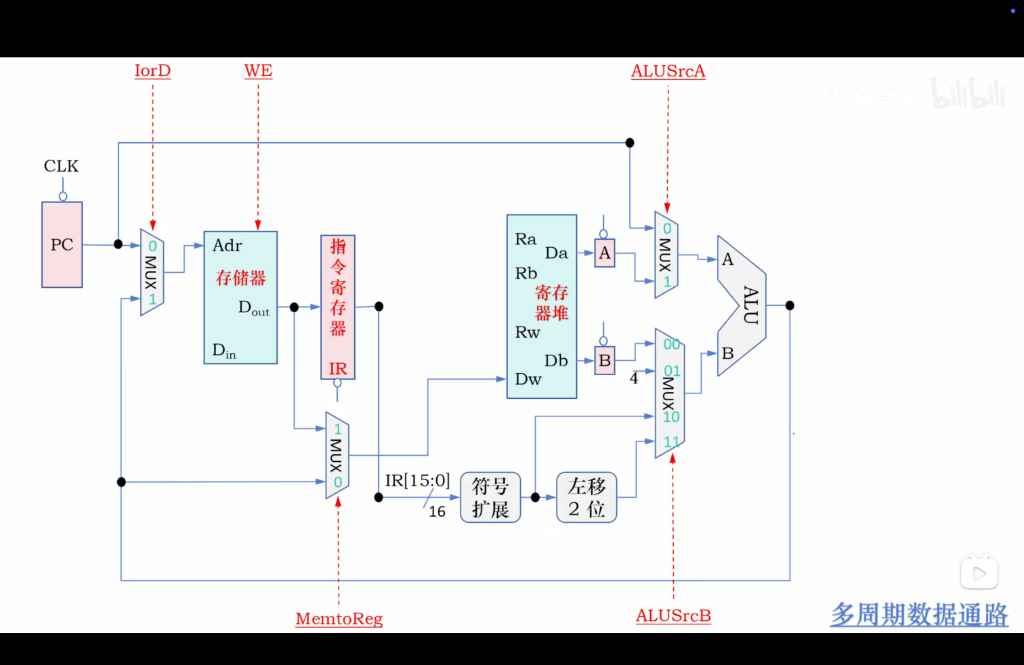

观察: > 通过多路选择器不用区分指令寄存器和数据寄存器了。

精确解读: 多周期CPU使用一个统一的存储器来同时扮演指令存储器和数据存储器的角色,而单周期CPU通常需要将它们物理分离。

-

单周期CPU的困境:在单周期设计中,一条

lw指令需要在同一个长周期内既要读取指令,又要访问数据。如果只有一个存储器,就会产生“结构性冲突”——存储器的一个端口在同一时间只能做一件事。因此,单周期CPU通常被描绘成拥有一个独立的指令存储器(Instruction Memory)和一个独立的数据存储器(Data Memory)。这在硬件上是昂贵且冗余的。 -

多周期CPU的智慧:多周期设计巧妙地利用了时间来解决这个冲突。

-

取指周期(Cycle 1):CPU总是先从存储器中读取指令。

-

访存周期(Cycle 4):只有

lw和sw等指令才需要再次访问存储器来读写数据。 -

由于“取指”和“访存”发生在不同的时钟周期,所以它们可以分时复用同一个存储器。

-

硬件实现:如图所示,一个由控制信号

IorD控制的MUX(多路选择器)被放在存储器的地址输入端。-

当

IorD = 0时,选择PC作为地址,此时存储器扮演指令存储器的角色。 -

当

IorD = 1时,选择ALU的计算结果(即数据地址)作为地址,此时存储器扮演数据存储器的角色。

-

-

结论:多周期CPU用一个MUX和分时复用的思想,整合了存储器资源,降低了硬件成本。

区别二:增加中间寄存器 (IR) vs. “一穿到底”

观察: > 多了一个IR(指令寄存器)相较于单周期CPU,这里是为什么?

精确解读: IR的出现是多周期设计的必然要求,因为指令的生命周期变长了。

-

单周期CPU的“瞬间记忆”:在单周期CPU中,指令从取指到执行完毕,所有数据就像电流一样“一穿到底”,在一个周期内流过整个数据通路。控制器和各个部件只需要在当前周期使用指令的各个字段,下个周期就是下一条新指令了,无需“记住”上一条指令。

-

多周期CPU的“持久记忆”:在多周期CPU中,一条指令的执行横跨多个时钟周期。

-

在取指周期(Cycle 1)结束后,

PC马上就要更新,为下一条指令的取指做准备。 -

如果此时不把当前指令保存下来,它的信息就会在Cycle 2开始时丢失!

-

硬件实现:为了解决这个问题,我们必须引入指令寄存器(Instruction Register, IR)。

IR是一个状态元件,它的作用是在Cycle 1结束时“锁存”从存储器读出的指令,并在后续的几个周期(译码、执行、访存、写回)中,为控制器和数据通路稳定地提供这条指令的二进制位。 -

同理,图中未画出的

A、B、ALUOut等也都是为跨周期传递数据而增设的中间寄存器。

-

结论:IR等中间寄存器的作用是**“状态保持”**,它们是连接多周期CPU各个执行阶段的桥梁,确保指令和数据在跨周期执行时不会丢失。

区别三:复用的ALU vs. 专用的计算单元

观察: > 多周期CPU只需要设置一个ALU,然后通过多路选择器来控制两个输入,具体讲讲这个选择的过程。

精确解读: 这是硬件复用思想最极致的体现。单周期CPU为了并行,需要多个计算单元;而多周期CPU则可以用一个ALU分时完成所有计算。

-

单周期CPU的“兵多将广”:单周期CPU为了在一个周期内完成所有任务,通常需要:

-

一个主

ALU用于R-type运算和lw/sw的地址计算。 -

一个独立的

加法器用于计算PC+4。 -

另一个独立的 加法器 用于计算分支跳转地址。

这些计算单元是同时工作的,是一种空间上的并行。

-

-

多周期CPU的“一夫当关”:多周期CPU可以用一个ALU分时完成上述所有工作。奥秘就在于ALU输入端的两个大型MUX(由

ALUSrcA和ALUSrcB控制)。ALU输入选择过程详解:

-

输入A的选择 (由

ALUSrcA控制)-

ALUSrcA = 0: 选择PC。这个路径在什么时候用?-

周期1 (取指):计算

PC+4,为顺序执行做准备。 -

周期3 (分支):计算分支目标地址

PC + (offset << 2)。

-

-

ALUSrcA = 1: 选择从寄存器堆读出的数据Ra(即rs的值)。什么时候用?-

周期2 (执行):对于R-type指令,这是第一个操作数。

-

周期3 (访存地址计算):对于

lw/sw指令,这是基地址。 -

周期2 (执行):对于

beq指令,这是被比较的第一个数。

-

-

-

输入B的选择 (由

ALUSrcB控制)-

ALUSrcB = 00: 选择从寄存器堆读出的数据Rb(即rt的值)。用于R-type指令和beq指令的计算。 -

ALUSrcB = 01: 选择常量4。配合输入A的PC,用于在周期1计算PC+4。 -

ALUSrcB = 10: 选择指令中IR[15:0]符号扩展后的立即数。用于lw/sw指令在周期3计算有效地址 (基地址 + 偏移量)。 -

ALUSrcB = 11: 选择立即数符号扩展并左移2位后的值。配合输入A的PC,用于beq指令在周期3计算分支目标地址。

-

-

结论:通过精巧的MUX设计和时序控制,多周期CPU让一个ALU在不同周期扮演不同角色,完美实现了计算单元的复用,大幅减少了硬件逻辑门的总量。

总结:单周期 vs. 多周期

| 特性 | 单周期CPU | 多周期CPU |

|---|---|---|

| 设计思想 | 空间并行,一步到位 | 时间并行,分步执行 |

| 时钟周期 | 长且固定(由最慢指令决定) | 短且固定 |

| CPI | 恒为 1 | 平均大于 1(不同指令周期数不同) |

| 存储器 | 指令/数据存储器物理分离 | 指令/数据存储器统一,分时复用 |

| 计算单元 | 多个专用ALU/加法器 | 单个通用ALU,分时复用 |

| 状态寄存器 | 无需(或很少) | 必须有IR等中间寄存器来跨周期存数 |

| 控制器 | 简单组合逻辑 | 复杂的时序逻辑(有限状态机) |

| 硬件成本 | 高(部件冗余) | 低(硬件复用) |

| 性能 | 低(时钟频率受限) | 较高(时钟频率提升) |