硬布线控制器:钢铁直男的绝对控制逻辑!💪

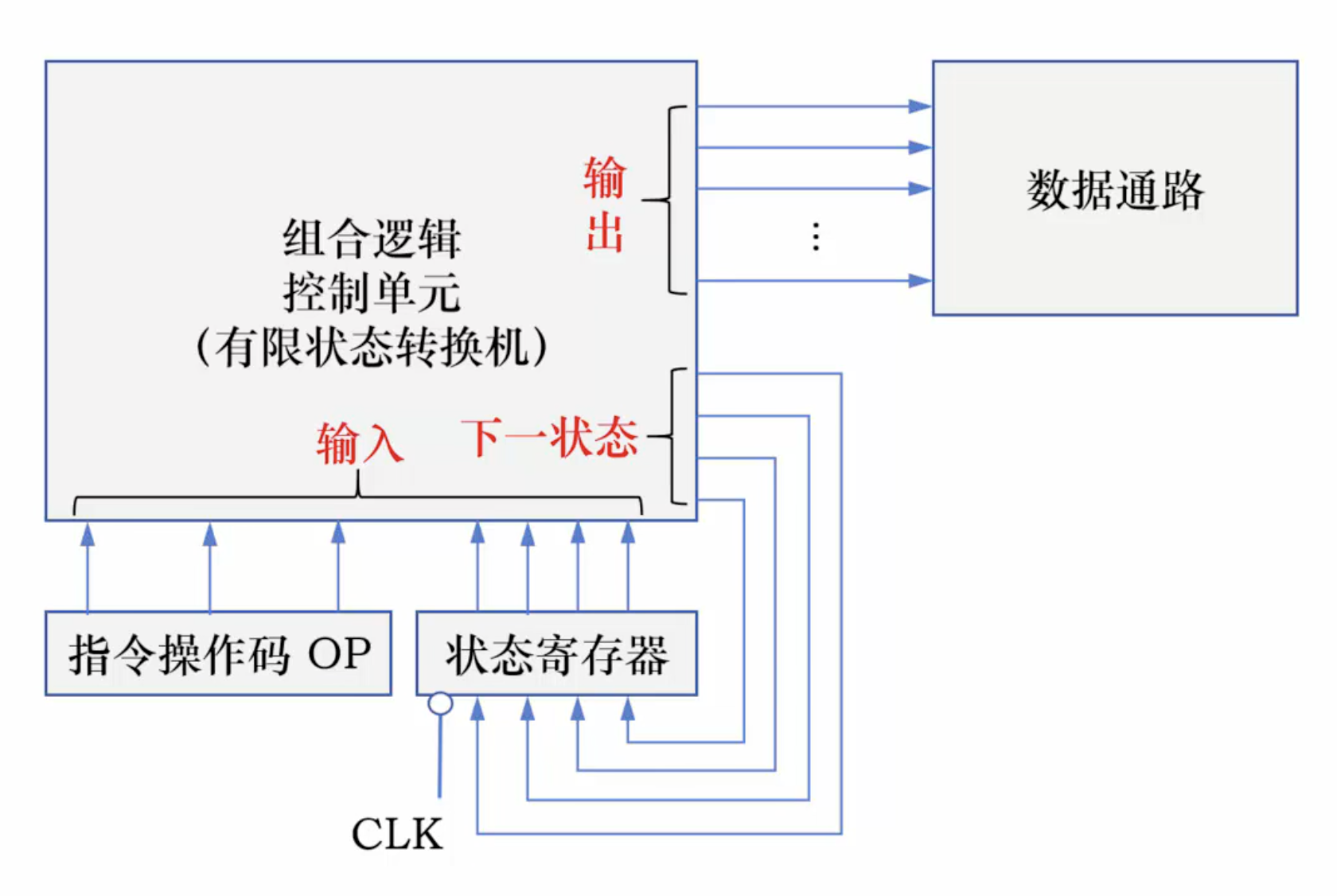

这张图展示的是**硬布线控制器(Hardwired Controller)**的核心结构

首先,我用一句话概括这张图的核心思想:

硬布线控制器本质上是一个有限状态机(FSM),它利用组合逻辑电路根据当前状态和外部输入(如指令操作码和状态标志),产生用于控制数据通路的微操作信号,并同时确定控制器的下一个状态。

2. 结合图示的详细实现逻辑讲解

这张图非常经典地展示了硬布线控制器的**有限状态机(Finite State Machine, FSM)**模型。我们可以把图中的各个部分拆解开来看:

(1) 核心部件解析

-

组合逻辑控制单元 (Combinational Logic Control Unit)

-

本质:这是硬布线控制器的“大脑”,它是一个纯粹的组合逻辑电路。这意味着它的输出在任何时刻都只取决于当前的输入。它没有记忆功能。

-

功能:它的功能可以分为两个部分,如其输出所示:

-

产生“输出”:根据输入产生当前周期需要发往数据通路的控制信号(例如:

PC_out,MAR_in,ALU_add,MemRead等)。 -

产生“下一状态”:根据输入决定 FSM 在下一个时钟周期应该进入的状态。

-

-

-

状态寄存器 (Status Register)

-

本质:这是一个由多个触发器(如D触发器)构成的寄存器,是整个控制器中唯一的记忆元件。

-

功能:它的作用是存储和提供有限状态机的**“当前状态”**。例如,如果状态寄存器有3位,那么控制器最多可以有 23=8 个不同的状态(S0, S1, ..., S7)。这些状态通常对应指令周期中的不同时间步(T状态),如

T0,T1,T2...

-

-

输入 (Inputs)

-

指令操作码 (OP):来自指令寄存器(IR)的操作码字段。它告诉控制器这条指令具体要做什么(如ADD, LOAD, JUMP),这决定了“执行周期”的状态序列。

-

当前状态:来自状态寄存器的输出。这是最重要的输入之一,它告诉组合逻辑电路“我们现在正处于指令周期的哪一步”。

-

外部状态/标志位 (图中未显式画出,但隐含存在):来自ALU的状态标志(如零标志Z、进位标志C、负标志N等)。这些标志用于实现条件转移指令(如 JZ, JC)。

-

-

时钟 (CLK)

- 功能:提供整个系统的同步“心跳”。在每个时钟脉冲的有效边沿(例如上升沿),状态寄存器会用“下一状态”的输出值来更新自己的内容,从而完成一次状态转换。

(22) 工作流程(一个时钟周期内发生的事)

让我们跟随信号的流动,来看控制器是如何循环工作的:

-

T时刻(时钟周期开始):

-

状态寄存器保存着当前状态 Scurrent,并将其作为输入稳定地提供给组合逻辑控制单元。 -

同时,指令的

OP码和ALU的标志位也作为输入提供给组合逻辑控制单元。

-

-

T时刻内(组合逻辑电路工作):

-

组合逻辑控制单元接收到 Scurrent、OP码和标志位后,立即根据其内部固化的逻辑(由与或非门实现)进行运算,并同时产生两组稳定的输出:-

一组是发往数据通路的控制信号。例如,如果当前状态是取指周期的T0状态,那么输出的控制信号可能就包括

PC_out(程序计数器的值送到总线)和MAR_in(总线的值送入内存地址寄存器)。 -

另一组是下一状态 Snext。例如,如果当前状态是T0,那么下一状态几乎总是T1。如果当前是执行JUMP指令的最后一步,下一状态就可能是T0,开始取下一条指令。

-

-

-

T+1时刻(下一个时钟脉冲到来):

-

在CLK信号的驱动下,

状态寄存器将组合逻辑单元已经准备好的下一状态Snext 锁存进来。 -

于是,Snext 成为了新的当前状态 Scurrent。

-

系统进入下一个时钟周期,重复上述第1步。

-

这个“当前状态 → 组合逻辑 → 产生控制信号和下一状态 → 时钟驱动 → 下一状态变为当前状态”的循环,不断驱动计算机执行一条又一条指令。

(3) 逻辑表达式举例

硬布线的“硬”就体现在其实现逻辑是固定的布线。例如:

-

某个控制信号的逻辑可以表示为布尔表达式:

PC_out = T0 + T_JUMP + ... (表示在T0状态或JUMP指令的某个状态时,PC_out信号有效)

-

下一状态的某一位(假设状态寄存器是3位 S2S1S0)的逻辑也可以表示为布尔表达式:

Next_S0 = (S2′S1′S0′) + ... (表示当前状态是S0(000)时,下一状态的第0位是1,以此类推)

3. 常考点分析、历年命题方式与陷阱

-

与微程序控制器的对比:这是最核心的考点。

-

硬布线:速度快,逻辑固定,指令系统不易修改。

-

微程序:速度慢,逻辑由控制存储器中的微程序定义,指令系统易修改、易扩展,设计更规整。

-

-

设计控制信号逻辑表达式:题目可能会给出一个简化的数据通路和几条指令,要求写出某个控制信号的逻辑表达式(如上例中的

PC_out)。 -

识别部件功能:考题可能会直接给出此图,询问“状态寄存器”的作用(记忆当前状态)或“组合逻辑单元”的输入来源等。

-

陷阱/易错点:

-

混淆“状态寄存器”与“程序状态字寄存器(PSW)”:图中的“状态寄存器”是控制器内部的,用于记录FSM的状态(T0,T1...)。而PSW是程序员可见的,用于记录运算结果的标志(Z,C,N...)。虽然PSW中的标志位会作为控制器的输入,但两者不是一回事。

-

认为组合逻辑有记忆功能:必须明确,记忆功能仅由“状态寄存器”这一时序部件提供。组合逻辑单元本身是无记忆的。整个控制器(组合逻辑+状态寄存器)是一个时序逻辑电路。

-