确定微指令地址的两种方法

一、微程序控制器:从指令到微操作

- 一句话概括:CPU执行一条机器指令的过程,被分解为执行一个微程序,这个微程序由多条微指令构成,每条微指令发出一组微命令,这些微命令最终驱动硬件完成具体的微操作。

关系图示:

┌────────────────────────┐

│ 机器指令 (如 ADD) │

└────────────┬───────────┘

↓ (解释执行)

┌────────────────────────┐

│ 微程序 (ADD的微程序) │

└────────────┬───────────┘

│ 存放在 "控存(CM)" 中

↓

┌─────────────────┬─────────────────┬─────────────────┐

│ 微指令 1 │ 微指令 2 │ ... │

└──────┬──────────┴──────┬──────────┴──────┬──────────┘

│ │ │

↓ ↓ ↓

┌────────┴───────┐ ┌────────┴───────┐ ┌────────┴───────┐

│ 微命令集合 1 │ │ 微命令集合 2 │ │ ... │

└────────┬───────┘ └────────┬───────┘ └────────┬───────┘

│ │ │

↓ ↓ ↓

┌────────┴───────┐ ┌────────┴───────┐ ┌────────┴───────┐

│ 微操作集合 1 │ │ 微操作集合 2 │ │ ... │

└────────────────┘ └────────────────┘ └────────────────┘

2. 微程序控制器基本工作流程

-

取指阶段:CPU从主存中取出一条机器指令,存入指令寄存器(IR)。这个过程本身也是由一个固定的“取指微程序”来完成的。

-

地址映射:指令寄存器(IR)中的操作码(OP)字段被送到一个起始和转移地址发生器(或称为微地址映射逻辑)。该部件根据操作码,生成这条指令对应的微程序的入口地址。

-

取微指令:将该入口地址送入微程序地址寄存器 (μPC 或 μMAR)。

-

执行微指令:根据μPC中的地址,从控存(CM)中读出相应的微指令,存入微指令寄存器 (μIR)。

-

产生控制信号:μIR中的操作控制字段经过译码后,产生出所需的微命令,控制CPU各功能部件完成相应的微操作。

-

确定后继地址:μIR中的顺序控制字段,结合CPU的状态标志等信息,通过地址转移逻辑,生成下一条微指令的地址,并送回μPC。

-

重复步骤4-6,直到当前微程序执行完毕。微程序最后一条微指令会引导CPU返回到“取指微程序”的开头,以执行下一条机器指令。

二、微指令的编码方式

微指令的操作控制字段如果每个比特位都直接对应一个微命令(称为直接控制法或水平型微指令),会导致微指令非常长,浪费宝贵的控存空间。因此,必须对其进行编码。

- 一句话概括:对微命令进行编码,可以用较少的位数表示更多的控制信息,从而缩短微指令长度,减小控存容量。

1. 编码方式

-

直接编码(水平型):每个比特位代表一个微命令。优点是并行性好,速度快;缺点是微指令字长过长。

-

字段编码(垂直型):将互斥的微命令(即在同一个CPU周期内不会同时出现的微命令)分在同一个字段中,用少量位数进行编码。例如,ALU有8种操作(加、减、与、或等),它们是互斥的,可以用3位编码(23=8)。执行时,需要通过译码器还原出具体的微命令。优点是指令字长短;缺点是削弱了并行能力,且需要译码电路导致速度稍慢。

-

混合编码:在实际设计中,通常采用以上两种方式的结合。

在第一张图中,操作控制字段 那一长串 1000...0010 就是经过编码后的结果。

三、寻址的艺术:后继微指令地址的确定

这是微程序控制器的核心和难点。如何高效、灵活地从一条微指令转移到下一条?我们结合你提供的两张图来详细分析。

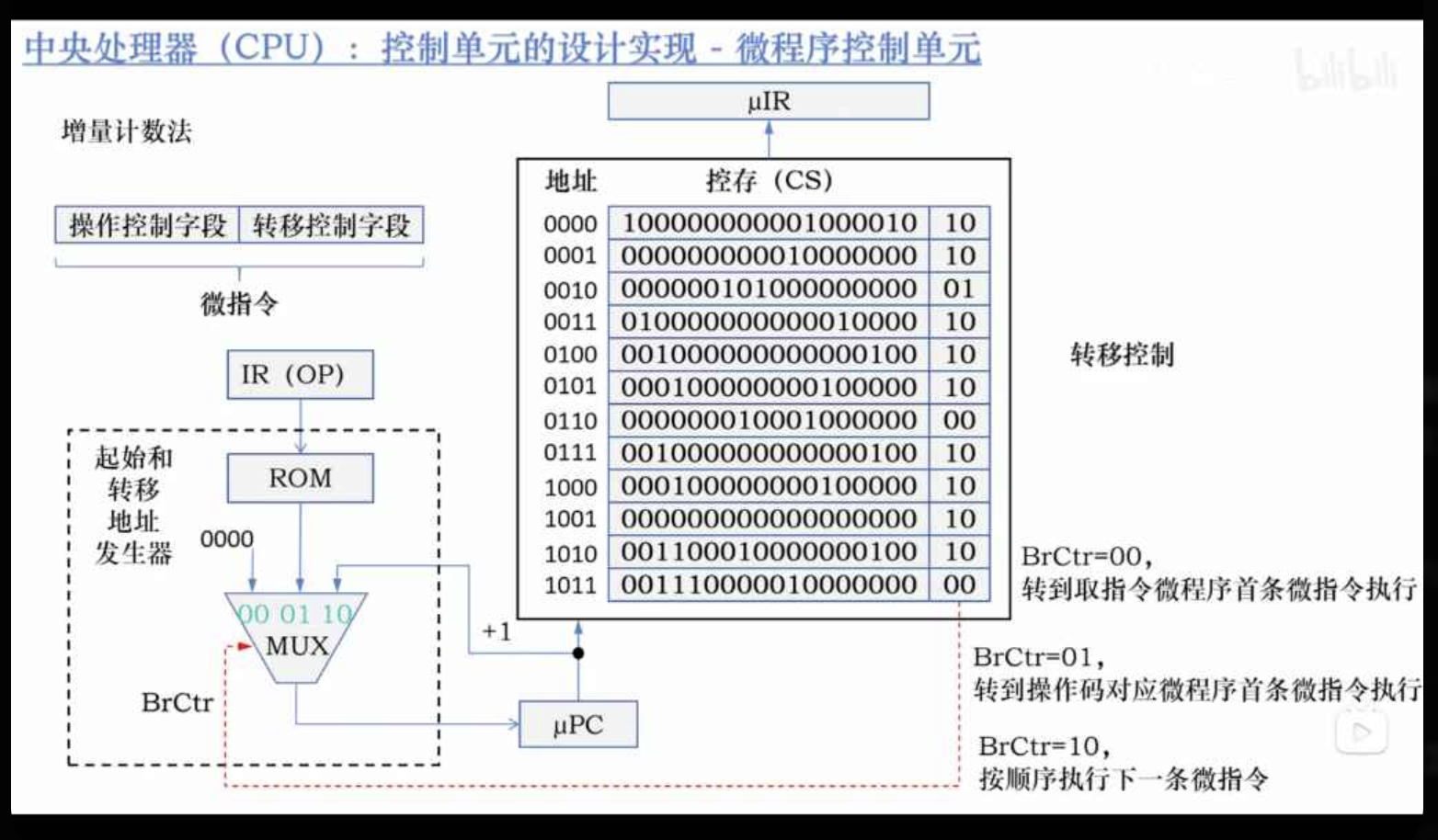

方式一:增量计数法 (Sequential + Branching)

这种方式是早期和基础的设计,其核心思想是**“顺序执行为主,转移执行为辅”**。

- 一句话概括:下一条微指令的地址通常是当前地址加1,仅在需要分支或跳转时,才通过转移控制字段指定新的地址。

原理与图解分析 (参考图一):

-

结构核心:在控制器中有一个微程序计数器 (μPC)。

-

默认操作:在大多数情况下,执行完当前微指令后,μPC会自动加1(

μPC <- μPC + 1),从而指向控存中的下一条微指令。这对应了图中μPC下方的+1逻辑。 -

转移控制:微指令中设置一个转移控制字段(或称判别测试字段,图中标记为

BrCtr)。该字段的值决定了是否要“打破”默认的+1规则。 -

图一中的

BrCtr逻辑分析:-

BrCtr = 10:按顺序执行。这是最常见的模式,此时选择μPC + 1的结果作为下一条微指令地址。 -

BrCtr = 00:无条件转移到取指微程序。这通常是一段微程序执行结束的标志。它会强制将一个固定的地址(通常是0000,即取指微程序的入口)载入μPC。 -

BrCtr = 01:按操作码转移。这发生在取指微程序结束之后。此时,会根据指令寄存器IR中的操作码IR(OP),通过地址产生器(图中的ROM)计算出对应指令(如ADD、SUB)的微程序的入口地址,并载入μPC。

-

优点:

-

微指令字长较短,因为不需要专门字段来存放下一条地址。

-

逻辑简单直观。

缺点:

- 存在冗余:如果多条不同的机器指令(如

ADD R1, (R2)和SUB R1, (R2))它们的微程序有共同的前缀部分(比如,都需要执行“计算(R2)的有效地址”这个微子程序),那么在控存中,这段相同的微指令序列需要被存储多次,造成空间浪费。

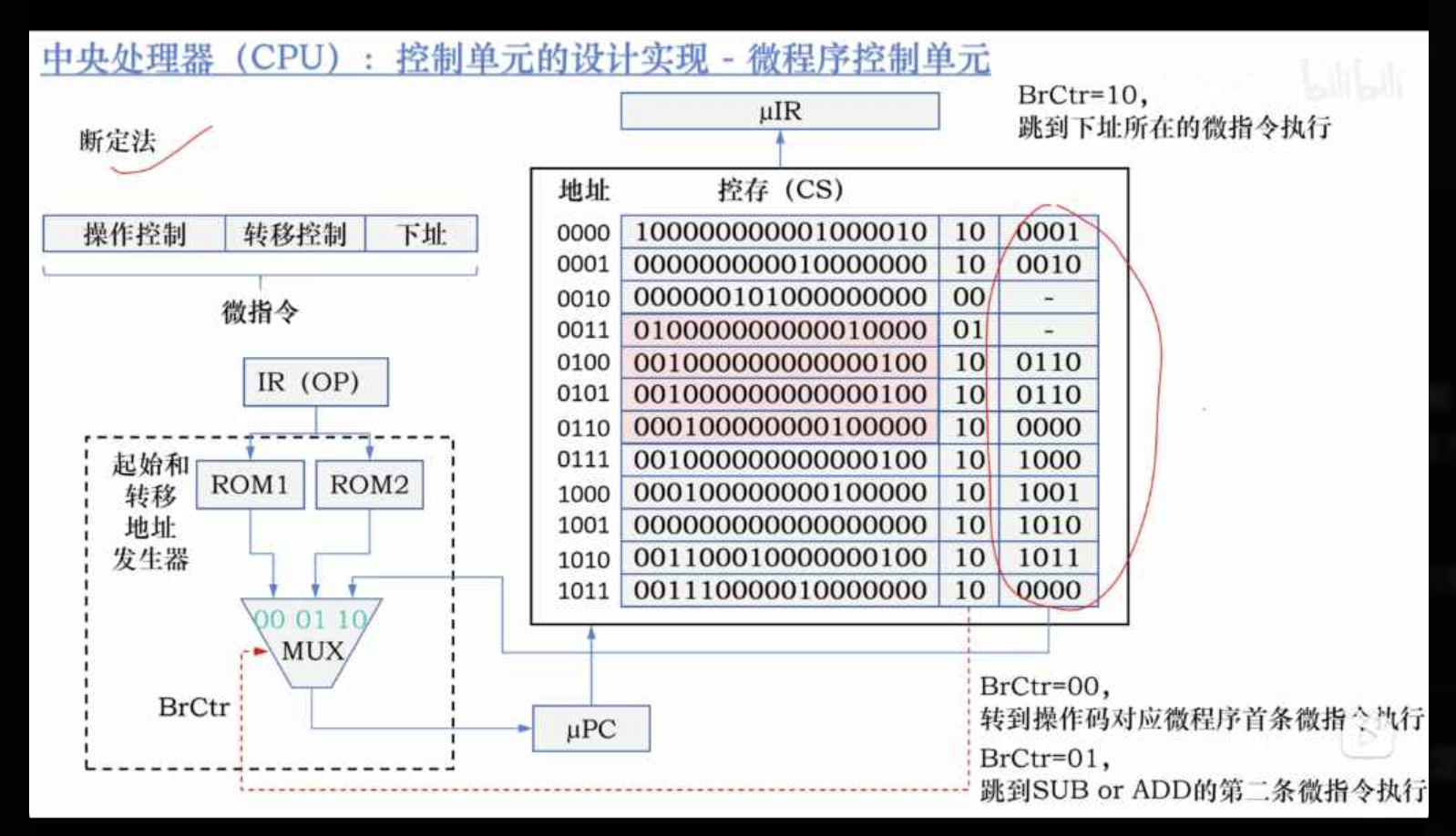

方式二:断定法 / 下地址字段法 (Dispatching / Two-Address Format)

为了解决增量法的冗余问题,引入了这种更为灵活的方式。其核心思想是**“每条微指令都明确指出下一条微指令的地址”**。

- 一句话概括:通过在每条微指令中增加一个“下地址”字段,直接给出后继微指令的地址,从而实现对公共微子程序的共享调用,节省控存容量。

原理与图解分析 (参考图二):

-

结构核心:微指令格式被扩展,增加了一个下地址字段。去除了μPC的自增

+1功能。 -

基本操作:在绝大多数情况下,下一条微指令的地址直接从当前微指令的下地址字段中获得。

-

转移控制:转移控制字段 (

BrCtr) 的作用变为“裁决”下一地址的来源,实现更复杂的多路转移(Multi-way Branch),这也是“断定法”名称的由来。 -

图二中的

BrCtr逻辑分析:-

BrCtr = 10:直接转移。将当前微指令的“下地址”字段的内容送入μPC。如图中地址0000的微指令,其下地址是0001,执行完0000后就跳到0001。 -

BrCtr = 00:无条件转移到取指微程序。和方式一类似,强制加载0000。 -

BrCtr = 01:断定转移 / 操作码多路转移。这是该方法最精髓的部分。它用于解决方式一的冗余问题。-

场景:假设所有指令的微程序第一步都是相同的(如公共的取数操作),存放在地址

P。执行完P之后,需要根据具体是ADD还是SUB指令,分别跳转到各自后续的微指令(比如ADD的第二步在地址A,SUB的第二步在地址B)。 -

实现:当

BrCtr=01时,地址转移逻辑会利用IR(OP)作为输入(如图中ROM1和ROM2),直接“断定”出下一条地址是A还是B,并载入μPC。这样,公共的微指令(地址P)只需要存储一份即可,ADD和SUB微程序共享了它,大大节省了控存空间。图中所示的“跳转到SUB或ADD的第二条微指令执行”就是这个意思。

-

-

优点:

-

通过共享微子程序,减少了控存中微指令的总条数,显著节省了控存容量。

-

执行流程更加灵活。

缺点:

-

微指令的字长增加了(因为多了个“下地址”字段)。

-

控制逻辑相对复杂。

总结对比

| 特性 | 增量计数法 | 断定法 (下地址字段法) |

|---|---|---|

| 后继地址来源 | 默认 μPC+1,特殊情况由转移字段指定 |

默认来自微指令的“下地址”字段,特殊情况由转移字段裁决 |

| μPC功能 | 计数器,具备 +1 功能 |

仅为地址寄存器,无 +1 功能 |

| 微指令字长 | 较短 | 较长(因有下地址字段) |

| 控存总容量 | 可能较大(因微指令冗余) | 可能较小(因共享微程序,总条数少) |

| 灵活性 | 较差 | 很高 |

关于两个ROM

“断定法”中双ROM的精确分工与协同

ROM1负责根据指令操作码(OP)生成微程序的“起始地址”,用于启动一个全新的指令周期;ROM2则负责在微程序执行中途,根据操作码(OP)实现多路分支,跳转到不同的“后续分支地址”。

详细解释与图解分析

我们再来看这张“断定法”的结构图,并结合图上BrCtr的具体注释来理解:

1. ROM1:起始地址映射器 (Initial Address Mapper)

-

职责:将输入的指令操作码(IR[OP]) 转换为其对应的微程序入口地址。

-

输入:

IR(OP)。 -

输出:对应微程序在控存(CS)中的第一条微指令的地址。

-

触发条件:根据图中的标注,当**

BrCtr = 00时,控制器执行“转到操作码对应的微程序首条微指令执行”的操作。这意味着多路选择器MUX会选择ROM1**的输出,将其送入微地址寄存器μPC。 -

工作流程:

-

取指周期结束,一条新的机器指令(如

ADD)放入IR。 -

控制逻辑(可能是取指微程序的最后一条微指令)产生

BrCtr = 00。 -

ADD指令的操作码送入ROM1。 -

ROM1输出

ADD微程序的入口地址(例如0100)。 -

该地址经MUX送入μPC,开始执行

ADD指令的微程序。

-

2. ROM2:断定/分支地址映射器 (Dispatch/Branch Mapper)

-

职责:实现微程序执行过程中的多路分支,这是节省控存空间的关键。

-

输入:

IR(OP)。 -

输出:在公共例程结束后,根据具体指令跳转到的不同分支的微指令地址。

-

触发条件:根据图中注释,当**

BrCtr = 01时,控制器执行“跳转到SUB或ADD的第二条微指令执行”。这清晰地表明,在执行完第一条(或前几条)公共微指令后,需要根据原始指令进行分流。此时,MUX会选择ROM2**的输出。 -

工作流程:

-

假设

ADD和SUB指令的微程序,第一步都是“取操作数”,这个公共操作的微指令地址为0100。 -

执行

0100地址的微指令,其BrCtr字段被设计为01。 -

原始指令的操作码(

ADD或SUB)送入ROM2。 -

如果操作码是

ADD,ROM2输出ADD第二步的地址(如1000);如果是SUB,输出SUB第二步的地址(如1001)。 -

该地址经MUX送入μPC,微程序流向各自专属的分支。

-

3. “下地址”字段:顺序执行的保障

-

职责:除了跳转,微程序更多时候是顺序执行的。在“断定法”中,这种“顺序”由微指令自带的**“下地址”字段**来指明。

-

触发条件:根据图中注释,当**

BrCtr = 10**时,执行“跳转到下址所在的微指令执行”。此时,MUX会选择从微指令寄存器(μIR)中直接送来的“下地址”字段的值。 -

这是“断定法”和“增量法”的根本区别:“增量法”的顺序执行靠

μPC+1,“断定法”的顺序执行靠微指令中的“下地址”字段。